# An Effective Design of Low Power Low Voltage Comparator using Complementary Metal-Oxide-Semiconductor Technology

<sup>1</sup> Aneesh S Perumprath, <sup>2</sup> Ajesh. F, <sup>3</sup> Praghash. K

<sup>1,</sup> Assistant Professor, Dept. of ECE, Musaliar College of Engineering and Technology, Pathanamthitta, Kerala, INDIA.

<sup>2</sup> Assistant Professor, Dept. of CSE, Musaliar College of Engineering and Technology, Pathanamthitta, Kerala, INDIA.

<sup>3</sup> Assistant Professor, Department of ECE, KL University, Green Fields, Vaddeswaram, Guntur District, A.P - 522 502, INDIA.

Abstract: - The requirement for ultra-low-control, region effective and fast simple tocomputerized converters is pushing toward the utilization of dynamic regenerative comparators to amplify speed and power proficiency. In this venture, an investigation on the deferral of the dynamic comparators will be displayed and diagnostic articulations are inferred. From the scientific articulations, fashioners can get an instinct about the principle supporters of the comparator delay and completely investigate the tradeoffs in unique comparator structure. In view of the displayed investigation, another dynamic comparator is proposed, where the circuit of a regular twofold tail comparator is adjusted for low-power and quick activity even in little supply voltages. Without confounding the structure and by including couple of transistors, the positive criticism amid the recovery is reinforced, which results in surprisingly decreased postpone time. Post-format re-enactment results in a 180 nm CMOS innovation affirm the examination results. It is appeared in the proposed dynamic comparator both the power utilization and postpone time are altogether diminished. The standard information control supply is at 1.2 V. Circuit can be structured in FinFET innovation to get further developed one.

Keywords: - Low power system, C-MOS Technology, Power converters, Comparator

# I. INTRODUCTION

Comparators are utilized to think about two voltages accessible at its information. When one information is higher than the other, at that point comparator circuit yield is in one state, and when the info conditions are turned around, at that point the comparator yield switches. Op-amp based comparators are control moderate in this way CMOS based comparators are the great decision over it. A dynamic comparator is not the same as Operation amp based comparator, since it gives yield just when client need to look at info voltages which makes it exceptionally control productive. Comparator is one of the central building obstructs in most simple to-advanced converters (ADCs)[1]. Numerous fast ADCs, for example, streak ADCs, require rapid, low power comparators with little chip zone. Rapid comparators in ultra-profound submicrometer (UDSM) CMOS advances experience the ill effects of low supply voltages particularly while considering the way that edge voltages of the gadgets have not been scaled at indistinguishable pace from the supply voltages of the

cutting edge CMOS forms. Thus, structuring fast comparators is all the more difficult when the supply voltage is littler. At the end of the day, in an offered innovation, to accomplish rapid, bigger transistors are required to repay the decrease of supply voltage, which likewise implies that more pass on zone and power is required.

Also, low-voltage task results in constrained regular mode input go, which is critical in some rapid ADC designs, for example, streak ADCs. Numerous strategies, for example, supply boosting methods, techniques [6] utilizing body-driven transistors current-mode plan and those utilizing double oxide forms, which can deal with higher supply voltages have been created to meet the low-voltage configuration challenges. Boosting and bootstrapping [6] are two procedures dependent on enlarging the supply, reference, or clock voltage to address input-range and exchanging issues. These are successful strategies; however they present dependability issues particularly in UDSM CMOS advances. Body-driven procedure [7] embraced by Blalock, evacuates the edge voltage necessity with the end goal that body driven MOSFET works as an exhaustion type gadget. In light of this methodology, in a 1-bit quantizer for modulators is proposed.

In spite of the points of interest, the body driven transistor experiences littler Trans conductance (equivalent to gmb of the transistor) contrasted with its door driven partner while unique creation process, for example, profound n-well is required to have both nMOS and pMOS transistors work in the body-driven configuration [2]. Aside from innovative changes, growing new circuit structures which abstain from stacking such a large number of transistors between the supply rails is best for low-voltage activity, particularly in the event that they don't expand the circuit multifaceted nature. In extra hardware is added to the regular dynamic comparator to upgrade the comparator speed in low supply voltages. The proposed comparator of works down to a supply voltage of 0.5 V. Regardless of the adequacy of this methodology, the impact of part confound in the extra hardware on the execution of the comparator ought to be considered. The structure of twofold tail dynamic comparator first proposed depends on planning a different information and cross coupled organize. This partition empowers quick task over a wide normal mode and supply voltage go.

#### II. RELATED WORK

The traditional dynamic comparator broadly utilized in A/D converters, with high information impedance, rail-to-rail yield swing, and no static power utilization .The activity of the comparator is as per the following: - During the reset stage when CLK = 0 and Mtail is off, reset transistors (M7– M8) pull both yield hubs Outn and Outp to VDD to characterize a begin condition and to have a substantial intelligent dimension amid reset. In the examination stage, when CLK = VDD, transistors M7 and M8 are off, and Mtail is ON[3]. Yield voltages (Outp, Outn), which had been pre-charged to VDD, begin to release with various releasing rates relying upon the relating input voltage (INN/INP)[1]. Accepting the situation where VINP > VINN, Outp releases quicker than Outn, consequently when Outp ( released by transistor M2 deplete current), tumbles down to VDD– |Vthp| before Outn (released by transistor M1 deplete current), the relating pMOS transistor (M5) will turn on starting the lock recovery brought about by back-toback inverters (M3, M5 and M4, M6)[4].

Ad hoc nodes energy consumption is a primary part to extend the network lifetime [8] suggested by K. Praghash *et al.* (2017). Based on clustering mechanisms life time of sensors and its energy consumption methods metrics of measuring is also vary. We may not modify the predefined WSN architectures, in the meantime some of the possibilities are there in between applications. An emblematic node has an inbuilt sensor system and this fully depending on applications (Sensor network application, Node application and Sensor application).

A customary twofold tail comparator topology has less stacking and in this way can work at lower supply voltages contrasted with the regular dynamic comparator. The twofold tail empowers both an extensive current in the locking stage and more extensive Mtail2, for quick hooking free of the info normal mode voltage, and a little present in the information arrange (little Mtail1), for low Offset [5].

K. Praghash *et al.* (2018) A multi-degree IP log table is utilized to distinguish the gate crashers at diverse ranges of the device [3]. Once the prompted range is found, the information is sent to multi-degree engineering to restrain the spreading of the stimulated region within the honeypot. This statistics will be dispatched to the honeypot to make a guard framework towards the attackers.

Dynamic comparator has low power utilization, since it has low action factor. Unmistakably diminishing charging and releasing rate (movement factor) will influence generally speaking exchanging power utilization of comparator. It is discovered that deferral of dynamic comparator likewise comprises of information differential voltage. To acquire voltage distinction between hub fp and fn two strategies can be proposed as pursues. Release hub fp and charge hub fn (however it builds action factor and consequently control utilization [5]. Releasing of hub fp will contradict releasing of hub fn and hub fn will increment releasing rate of hub fp (proposed).The proposed configuration utilizes second hub release strategy, by expelling cross coupled inverter match from ordinary dynamic comparator the movement factor is discovered decreased.

In [6] an efficient modified routing algorithm is presented by K. Praghash *et al.* (2018) to select the cluster head nearer to the sink next hop. So that, in case of the bottleneck, the nodes are capable of determining the best possible routes with higher energy nodes for data transmission. Since the protocols utilized by the WSNs are application oriented; three classes such as data-centric, hierarchical and location-based classes are investigated.

# III. PROPOSED METHOD

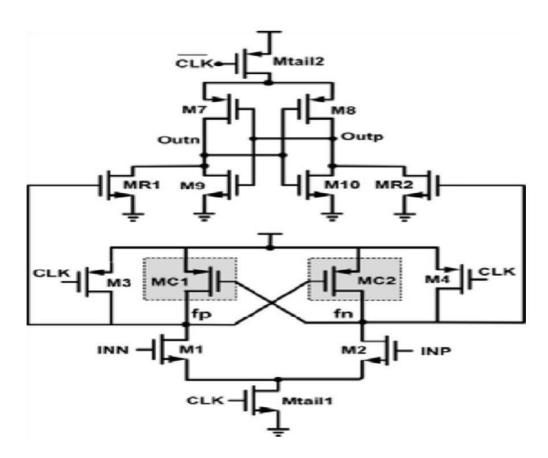

Because of the better execution of twofold tail engineering in low-voltage applications, the proposed comparator is planned dependent on the twofold tail structure as appeared in figure 1. The primary thought of the proposed comparator is to build Vfn/fp so as to expand the hook recovery speed. For this reason, two control transistors (Mc1 and Mc2) have been added to the main stage in parallel to M3/M4 transistors however in a cross-coupled way. This thusly upgrades  $\Delta V0$  which prompts expanded lock recovery speed or decreased postpone time.

In structuring the proposed comparator, some plan issues must be considered. While deciding the extent of tail transistors (Mtail1 and Mtail2), it is important to guarantee that the time it takes that one of the control transistors turns on must be littler than t0 (beginning of recovery) This condition can be effectively accomplished by appropriately planning the first and second stage tail flows. Regardless of whether conceivable in the manufacture innovation, low-edge pMOS gadgets can be utilized as control transistors prompting quicker turn on. In structuring the nMOS switches, situated beneath the information transistors, the deplete source voltage of these switches must be considered since it may confine the voltage headroom, limiting the upside of being utilized in low-voltage applications. So as to lessen this impact, low-on obstruction nMOS switches are required.

As it were, extensive transistors must be utilized. Since the parasitic capacitances of these switches don't influence the parasitic capacitances of the fn/fp hubs (postpone bottlenecks), it is conceivable to ideally choose the measure of the nMOS switch transistors such that both low-voltage and low-control tasks are kept up.

Fig.1 Schematic system design

# IV. DESIGN CONSIDERATIONS

While deciding the measure of tail transistors (Mtail1 and Mtail2), it is important to guarantee that the time it takes that one of the control transistors turns on must be littler than t0 (beginning of recovery) This condition can be effectively accomplished by legitimately structuring the first and second stage tail currents[9]. Regardless of whether conceivable in the manufacture innovation, low-edge pMOS gadgets can be utilized as control transistors prompting quicker turn on.

In planning the nMOS switches, situated beneath the information transistors, the deplete source voltage of these switches must be considered since it may confine the voltage headroom, limiting the benefit of being utilized in low-voltage applications [8]. So as to lessen this impact, low-on-opposition nMOS switches are required. At the end of the day, huge transistors must be utilized. Since the parasitic capacitances of these switches don't influence the parasitic capacitances of the fn/fp hubs (defer bottlenecks), it is conceivable to ideally choose the span of the nMOS switch transistors such that both low-voltage and low-control activities are kept up. The impact of jumble between controlling transistors on the absolute info alluded counterbalance of the comparator is another imperative issue. While deciding the extent of controlling transistors (MC1 – MC2), two essential issues ought to be considered.

1) The impact of edge voltage confuse and current factor jumble of the controlling transistors on the comparator input-alluded balance voltage.

2) The impact of transistor estimating on parasitic capacitances of the fn/fp hubs, i.e., CL,fn(p), and therefore the postponement of the comparator. While bigger transistors are required for better coordinating; be that as it may, the expanded parasitic capacitances are postpone bottlenecks

# V. EXPERIMENTAL RESULTS

The proposed VLSI architecture is simulated using LT SPICE. In order to compare the proposed comparator with the conventional and double-tail dynamic comparators, all circuits have been simulated in a  $0.18 \ \mu m$  CMOS technology with VDD = 1.2 V. The output waveform of dynamic, conventional double tail, existing and proposed comparator is shown in the figures below. From the analysis it is known that the proposed comparator consumed less power. The power consumption has been reduced significantly in the modified comparator. The delay of this comparator is reduced significantly.

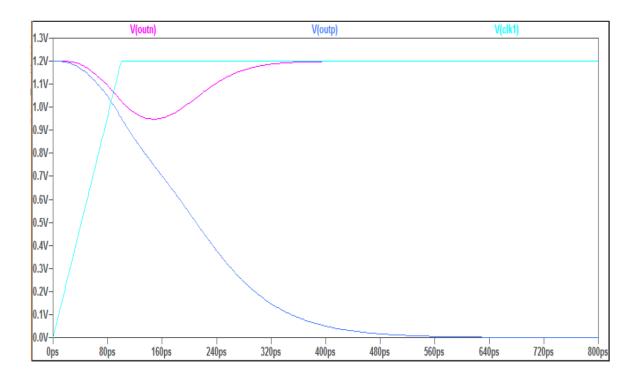

Fig. 2 Transient simulation of conventional dynamic comparator

Figure2 Shows the simulation result of conventional dynamic comparator, from the graph we can see that V(out n)start discharging and return backs to charging when m5 turn ON.V(out p) continue discharging and reaches to 0 V[10]. The delay of the above comparator consists of two delay t0 and t latch where to discharging delay of the load capacitance Cl and t latch is the latching delay of the cross coupled inverter and hence the total delay(t delay)[11].

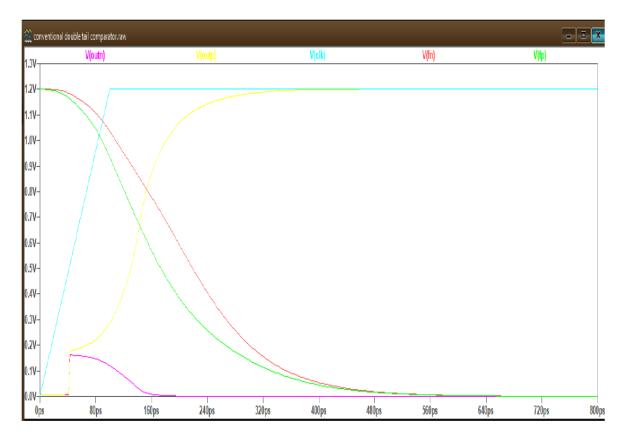

Fig. 3 Transient simulation of modified DTC

The delay of the double-tail dynamic comparator comprises of two delay t0 and t latch. Which is similar to that of conventional dynamic comparator [12]. Here t0 is the capacitive charging of the capacitance at the load C Lout (at the out*n* and out*p*) until the transistor (M9/M10) are on, and hence the latch regeneration starts and t0 is determined.

| Comparator<br>structure  | Conventional<br>dynamic<br>comparator | Double tail<br>dynamic<br>Comparator | Modified<br>DTC | Proposed<br>Structure |

|--------------------------|---------------------------------------|--------------------------------------|-----------------|-----------------------|

| CMOS<br>technology       | 180nm                                 | 180nm                                | 180nm           | 180nm                 |

| Supply<br>voltage        | 1.2V                                  | 1.2V                                 | 1.2V            | 1.2V                  |

| Power                    | 1.2268µW                              | 1.1241µW                             | 604.13nW        | 40.12nW               |

| Energy per<br>conversion | 0.98147fJ                             | 0.89921Fj                            | 0.48331fJ       | 0.032096fJ            |

| Time delay               | 214.53ps                              | 158.892ps                            | 84.0795ps       | 45.13ps               |

| No of<br>transistor      | 8                                     | 12                                   | 14              | 16                    |

#### TABLE OF COMPARISON

#### VI. CONCLUSION

This paper proposed a far reaching postpone investigation for timed dynamic comparators. Two normal structures of traditional dynamic comparator and customary twofold tail dynamic comparators were broke down. Additionally, in light of hypothetical investigations, another dynamic comparator with low-voltage low-control capacity was proposed so as to enhance the execution of the comparator. Post-design recreation results in 0.18-µm CMOS innovation affirmed that the postponement and vitality per transformation of the proposed comparator is decreased, as it were, in correlation with the regular dynamic comparator and twofold tail comparator. Twofold tail dynamic comparator configuration is introduced in this venture to improve hook recovery speed. The structure of hook organize is changed by including cross coupled transistors which prompts decrease in postpone time. The reproduction results affirm decrease in EPC just as absolute defer time for proposed DoTDC when contrasted with some current twofold tail dynamic comparators. Proposed comparator has supply voltage of 1.2V with absolute postponement of 45.13pS and EPC of 0.032096fJ.

#### References

- [1] B.Goll and H. Zimmermann, (2009) "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 11, pp. 810–814.

- [2] S.U. Ay, (2011) "A sub-1 volt 10-bit supply boosted SAR ADC design in standard CMOS" Int. J. Analog Integr. Circuits Signal Process., vol. 66, no. 2, pp. 213–221.

- [3] Praghash, K., Masthan, M., & Ravi, R. (2018). AN INVESTIGATION OF SECURITY TECHNIQUES FOR CONCEALED DDOS EXPOSURE ATTACKS. ICTACT Journal on Communication Technology, 9(1).

- [4] Dinabandhu Nath Mandal, (2004) "Analysis and Design of Low Voltage Low Power Dynamic Comparator with Reduced Delay and Power"*IJERGS Volume 2, Issue 3 ISSN 2091-2730*

- [5] Rahul Jain, (oct 2017) "Design of Low-Power High-Speed Double-Tail Dynamic CMOS Comparator using Novel Latch Structure" *UPCON*.

- [6] Praghash, K., & Ravi, R. (2018). Physical-traffic attentive vigorous routing (P-TAVR) and hot-spot detection to reduce the bottleneck in WSN. Cluster Computing, 1-12.

- [7] Amol D. Shinde, (2017)" Low Power, Area Efficient Dynamic Comparator with Reduced Activity Factor" *ICICIC*

- [8] Praghash, K., & Ravi, R. (2017, March). Energy consumption architecture for wireless sensor networks with different clusters. In Science Technology Engineering & Management (ICONSTEM), 2017 Third International Conference on (pp. 414-418). IEEE.

- [9] A.Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay,(2010) "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in *Proc. IEEE Int. Midwest Symp. Circuits Syst. Dig. Tech. Papers*, pp. 893–896.

- [10] B.J.Blalock,(2000) "Body-driving as a Low-Voltage Analog Design Technique for CMOS technology," in *Proc. IEEE Southwest Symp. Mixed-Signal Design*, pp. 113–118.

- [11] M.Maymandi-Nejad and M. Sachdev,(2003) "1-bit quantiser with rail to rail input range for sub-1V \_\_\_\_\_\_ modulators," *IEEE Electron. Lett.*, vol. 39, no. 12, pp. 894–895.

- [12] Y.Okaniwa, H. Tamura, M. Kibune, D. Yamazaki, T.-S. Cheung, J. Ogawa, N. Tzartzanis, W. W. Walker, and T. Kuroda, (2005) "A 40Gb/s CMOS clocked comparator with bandwidth modulation technique," *IEEE J. Solid-State Circuits*, vol. 40, no. 8, pp. 1680–1687.

- [13] B.Goll and H. Zimmermann,(2007) "A 0.12 μm CMOS comparator requiring 0.5V at 600MHz and 1.5V at 6 GHz," in Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers,, pp. 316–317.

- [14] B.Goll and H. Zimmermann,(2000) "A 65nm CMOS comparator with modified latch to achieve 7GHz/1.3mW at 1.2V and 700MHz/47μW at 0.6V," in Proc. IEEE Int. Solid-State Circuits Conf. Dig. Tech. Papers,pp. 328–329.

- [15] D.Shinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, (2007) "A double-tail latch-type voltage sense amplifier with 18ps Setup+Hold time," in *Proc. IEEE Int. Solid-State Circuits Conf.*, *Dig. Tech. Papers*, pp. 314–315.