# DESIGN OF LOW POWER HIGH SPEED CASCADED DOUBLE TAIL COMPARATOR

B.Manoj Kumar<sup>1</sup>, Dr.N.Muthu Kumaran<sup>2</sup>

PG Student, VLSI Design, Francis Xavier Engineering College, Tirunelveli, Tamilnadu, India<sup>1</sup>

Assistant Professor, Department of ECE, Francis Xavier Engineering College, Tirunelveli, Tamilnadu, India<sup>2</sup>

#### Abstract:

Comparator is an important element in many Data converter circuits, Signal processing systems, such as telecommunication interfaces and in the sensory circuits. Also comparators are the basic building elements for designing modern analog and mixed signal systems. Many high speed analog to digital converters, such as Flash ADCs, require low power, high speed comparators with small chip area. In this paper, a novel new double tail comparator which consumes very less power and can operate at high speeds when compared to the existing double tail comparators is proposed and simulated. Because of its high speed and low power consumption it can be used in high speed analog to digital converters, such as Flash ADCs requiring low power, high speed comparators. The designed double tail comparator is simulated using Cadence virtuoso tool with 180nm technology. From the simulation results, it is observed that in the proposed double tail comparator both the power consumption and delay time are significantly reduced.

Keywords:- Double-tail comparator, Clocked Regenerative Comparator, Positive feedback, Switching transistor.

#### I. INTRODUCTION

One of the most important basic building blocks in analog and mixed-mode circuits is the comparator. The function of a CMOS comparator is to compare an input signal with a reference signal and produce a binary signal output. Comparator uses back to back cross coupled inverters to convert the voltage into digital output in a short period of time. The performance of the comparator plays an important role in realization of high integration, low power, low cost and good design.

Designing high-speed comparators is more challenging when the supply voltage becomes smaller [2]. In other words, in a given technology, to achieve high speed, larger transistors are required to compensate for the reduced supply voltage. It also means that more die area and power is needed. Besides, low-voltage operation results in limited common-mode input range, which is important in many high-speed ADC architectures, such as Flash ADCs.

Clocked regenerative comparators have found wide applications in many high-speed analog to digital convertors (ADCs) because of their fast decisions due to the strong positive feedback in the regenerative latch. The recent comprehensive analyses investigate the performance of these

comparators from different aspects, such as noise, offset, random decision errors and kick-back noise [5].

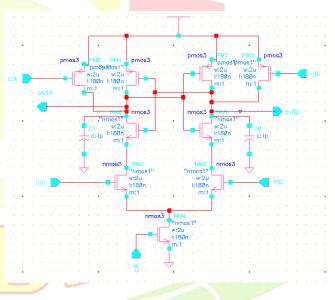

## **II. CONVENTIONAL DYNAMIC COMPARATOR**

Conventional dynamic comparator is widely used in A/D converters. The comparator has high input impedance, rail-to-rail output swing, and has no static power consumption. The schematic diagram of the conventional dynamic comparator is shown in fig 1.

The operation of the conventional dynamic comparator is explained below.

During the reset phase when CLK = 0 and  $M_{tail}$  is off, the reset transistors  $M_7$  and  $M_8$  pull both the output nodes Outn, Outp to VDD to define a start condition and to have a valid logical level during the reset.

In the comparison phase, when CLK = V<sub>DD</sub>, transistors M<sub>7</sub>, Ms are off and M<sub>tail</sub> is on. Output nodes (Outp, Outn) which had been pre-charged to V<sub>DD</sub>, start to discharge at different discharging rates depending on the corresponding input voltages (V<sub>INP</sub>, V<sub>INN</sub>). Assuming the case where V<sub>INP</sub> > V<sub>INN</sub>, the output node Outp discharges faster than Outn, hence with Outp (discharged by transistor M<sub>2</sub> drain current), falling down to V<sub>DD</sub>-|V<sub>thp</sub>| before Outn (discharged by transistor M<sub>1</sub> drain current), the corresponding PMOS transistor (M<sub>5</sub>) will turn on to initiate the latch regeneration caused by back-to-back inverters (M<sub>3</sub>-M<sub>5</sub> and M<sub>4</sub>-M<sub>6</sub>). Thus, the output node Outn pulls to V<sub>DD</sub> and Outp discharges to ground. If the input voltage V<sub>INP</sub> is less than V<sub>INN</sub>, the circuit works vice versa.

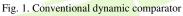

#### III. CONVENTIONAL DOUBLE TAIL COMPARATOR

The schematic of conventional double tail comparator is shown in the fig 2. This structure has less stacking and therefore can operate at lower supply voltages compared to the conventional dynamic comparator.

The double tail enables both a large current in the latching stage and wider Mtail2, for fast latching independent of the input common-mode voltage ( $V_{cm}$ ), and a small current in the input stage (small Mtail1), for low offset.

The operation of the conventional double tail comparator is as follows.

During the reset phase (CLK = 0,  $M_{tail1}$  and  $M_{tail2}$  are off), c transistors M<sub>3</sub>,M<sub>4</sub> pre-charge the nodes fn and fp to V<sub>DD</sub>, which in turn make M<sub>R1</sub> and M<sub>R2</sub> to discharge the output nodes Outn and Outp to the ground.

During decision-making phase (CLK = VDD, Mtaill and Mtail2 turn on), the transistors M<sub>3</sub>,M<sub>4</sub> turn off and the voltages at nodes fn, fp start to drop with the rate defined by I Mtail1/Cfn(p) and an input-dependent differential voltage  $\Delta V$ fn(p) will also build up. The intermediate stage formed by the transistors MR1 and MR2 passes  $\Delta V$ fn(p) to the cross coupled inverters and provides a good shielding between to input and output to get a reduced value of kickback noise.

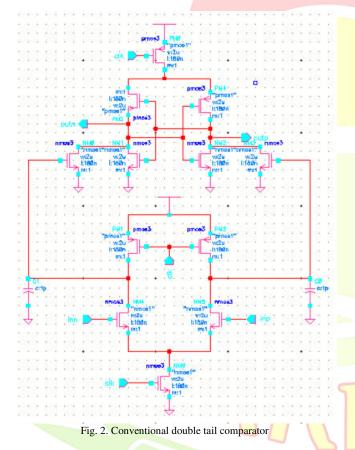

## IV. MODIFIED DOUBLE TAIL COMPARATOR

The modified double tail comparator is designed based on the double tail architecture. Fig.3 shows the schematic diagram of the modified double tail comparator.

Fig. 3. Modified double tail comparator

The idea of this comparator is to increase  $\Delta V_{\text{fn/fp}}$  in order to increase the latch regeneration speed. For this purpose, Mc1 and Mc2 are the two control transistors that have been added to the first stage in parallel to M<sub>3</sub>/M<sub>4</sub> transistors but in a cross-coupled manner [3].

The operation of the modified double tail comparator is as follows. During reset phase (CLK = 0, Mtail1 and Mtail2 are off, avoiding static power), M3 and M4 pulls both fn and fp nodes to Vpp, hence transistor  $M_{c1}$  and  $M_{c2}$  are cut off. Intermediate stage transistors, MR1 and MR2, reset both latch outputs to ground.

During decision-making phase (CLK = V<sub>DD</sub>, M<sub>tail1</sub>, and M<sub>tail2</sub> are on), transistors M<sub>3</sub> and M<sub>4</sub> turn off. Furthermore, at the beginning of this phase, the control transistors are still off (since f<sub>n</sub> and f<sub>p</sub> are about V<sub>DD</sub>). Thus, f<sub>n</sub> and f<sub>p</sub> start to drop with different rates according to the input voltages. Suppose V<sub>INP</sub> > V<sub>INN</sub>, thus f<sub>n</sub> drops faster than f<sub>p</sub>, (since M<sub>2</sub> provides more current than M<sub>1</sub>). As long as f<sub>n</sub> continues falling, the corresponding PMOS control transistor (M<sub>c1</sub> in this case) starts to turn on, pulling f<sub>p</sub> node back to the V<sub>DD</sub>; so another control transistor (M<sub>c2</sub>) remains off, allowing fn to be discharged completely. In other words, unlike conventional double-tail dynamic comparator, in which  $\Delta V_{fn/fp}$  is just a

function of input transistor trans conductance and input voltage difference, in the existing double tail structure as soon as the comparator detects that for instance node  $f_n$  discharges faster, a PMOS transistor (M<sub>c1</sub>) turns on, pulling the other node  $f_p$  back to the V<sub>DD</sub>. Therefore by the time passing, the difference between  $f_n$  and  $f_p$  ( $\Delta V_{fn/fp}$ ) increases in an exponential manner, leading to the reduction of latch regeneration time.

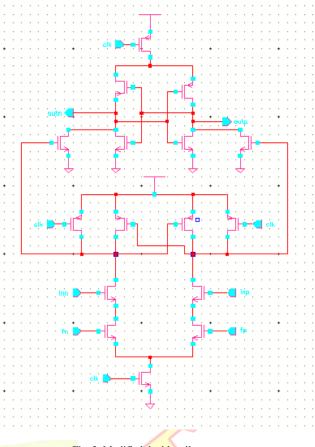

## V. CASCADED DOUBLE TAIL DYNAMIC COMPARATOR

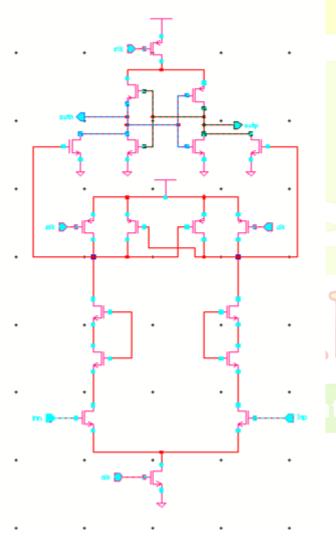

The cascaded double tail comparator is designed based on the existing double tail architecture due to its better performance in the low voltage applications. Fig.4 shows the schematic diagram of the cascaded double tail comparator.

The idea of this comparator is to reduce the total power consumption of the circuit. For this purpose,  $M_{n1}$  and  $M_{n2}$  are the two switching transistors that have been added to the second stage in series to  $M_1/M_2$  transistors.

The operation of the proposed double tail comparator is as follows. During the reset phase (CLK = 0,  $M_{tail1}$  and  $M_{tail2}$  are off, avoiding static power), M<sub>3</sub> and M<sub>4</sub> pulls both fn and fp nodes to VDD. Intermediate stage transistors, M<sub>R1</sub> and M<sub>R2</sub>, reset both latch outputs to ground.

During decision-making phase when CLK = VDD, Mtail1, and Mtail2 are on and transistors M3 and M4 are turned off, since fn and fp are about VDD. Thus, the nodes fn and fp start to drop with different rates according to the input voltages. Suppose if  $V_{INP} > V_{INN}$ , thus fn drops faster than fp, (since M<sub>2</sub> provides more current than M<sub>1</sub>). As long as fn continues falling, the corresponding PMOS transistor (M<sub>3</sub> in this case) starts to turn on, pulling f<sub>p</sub> node back to the VDD; so another transistor (M4) remains off, allowing fn to be discharged completely. In other words, unlike the conventional double tail dynamic comparator, in which  $\Delta V_{\text{fn/fp}}$  is just a function of input transistor transconductance and input voltage difference, in the proposed double tail structure as soon as the comparator detects that for instance node fn discharges faster, the PMOS transistor (M<sub>3</sub>) turns on, pulling the other node f<sub>p</sub> back to the VDD. Therefore by the time passing, the difference between fn and  $f_p(\Delta V_{fn/fp})$  increases in an exponential manner, reducing the latch regeneration time.

With this structure, the average power consumption of the circuit is reduced when compared to the existing double tail comparator.

### VI. SIMULATION RESULTS

The proposed circuit was simulated using CADENCE Virtuoso tool with 180nm technology. The supply voltage used in simulation is 0.8 volt. The simulation results of all the comparators are shown below.

Fig. 5. Simulation Result of Conventional Dynamic Comparator

Fig. 7. Simulation Result of Modified Double Tail Dynamic Comparator

Fig. 8. Simulation Result of Cascaded Double Tail Dynamic Comparator

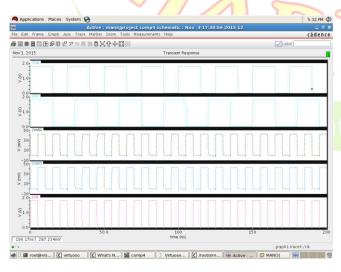

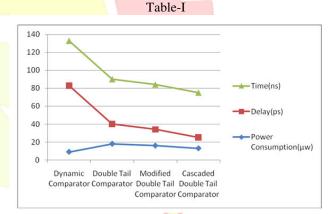

# VII. PERFORMANCE COMPARISON

The performance comparison given in table-I shows the average power dissipation and delay of all the discussed comparators.

| Technique<br>Used                     | Power<br>Consumption(µw) | Delay(ps) | Time(ns) |

|---------------------------------------|--------------------------|-----------|----------|

| Dynamic<br>Comparator                 | 11.452                   | 74.24     | 50       |

| Double Tail<br>Comparator             | 18.821                   | 22.62     | 50       |

| Modified<br>Double Tail<br>Comparator | 16.865                   | 18.56     | 50       |

| Cascaded<br>Double Tail<br>Comparator | 13.902                   | 15.32     | 50       |

Fig. 8. Power, Delay and Time Analysis graph

## VIII. CONCLUSION

In this paper, a comprehensive analysis of power and delay for clocked dynamic comparators were done. Based on the analysis, a new dynamic double tail comparator with low voltage, low power capability was proposed to improve the performance of comparator, mainly concerned in power consumption. Post layout simulation results in 180 nm CMOS technology confirm that the power consumption of the proposed comparator is reduced to a great extent in comparison with all other dynamic comparators. A novel cascaded double tail comparator is designed and simulated using 180nm CMOS technology. From the simulated results it is observed that the delay of the cascaded double tail comparator is 15.32ps which is comparatively less than the earlier comparators. Also the average power consumption of the proposed double tail comparator is calculated as 13.90µW.

#### REFERENCES

- [1] Samaneh Babayan-mashhadi, And Reza Lotfi, "Analysis And Design Of A Low-voltage Low-power Double-tail Comparator", *IEEE Trans.* on Very Large Scale Integration (Vlsi) Systems, 2013

- [2] B. Wicht, T. Nirschl, and D. Schmitt-Landsiedel, "Yield and speed optimization of a latch-type voltage sense amplifier," IEEE J. Solid-State Circuits, vol. 39, pp. 1148-1158, July 2004.

- [3] A. Mesgarani, M. N. Alam, F. Z. Nelson, and S. U. Ay, "Supply boosting technique for designing very low-voltage mixed-signal circuits in standard CMOS," in Proc. *IEEE Int. Midwest Symp. Circuits Syst.Dig. Tech. Papers*, Aug. 2010, pp. 893–896.

- [4] P. M. Figueiredo and J. C. Vital, "Kickback noise reduction technique for CMOS latched comparators," *IEEE Trans. Circuits Syst. II, Exp.Briefs*, vol. 53, no. 7, pp. 541–545, Jul. 2006

- [5] B. Goll and H. Zimmermann, "A comparator with reduced delay time in 65-nm CMOS for supply voltages down to 0.65," *IEEE Trans. Circuits Syst. II, Exp. Briefs*, vol. 56, no. 11, pp. 810–814, Nov. 2009.

- [6] S. U. Ay, "A sub-1 volt 10-bit supply boosted SAR ADC design in standard CMOS," *Int. J. Analog Integr. Circuits Signal Process.*, vol. 66, no. 2, pp. 213–221, Feb. 2011.

- [7] B. J. Blalock, "Body-driving as a Low-Voltage Analog Design Technique for CMOS technology," in *Proc. IEEE Southwest Symp. Mixed-Signal Design*, Feb. 2000, pp. 113–118.

- [8] M. Maymandi-Nejad and M. Sachdev, "1-bit quantiser with rail to rail input range for sub-1V \_\_ modulators," *IEEE Electron. Lett.*, vol. 39, no. 12, pp. 894–895, Jan. 2003.

- [9] D. Shinkel, E. Mensink, E. Klumperink, E. van Tuijl, and B. Nauta, "A double-tail latch-type voltage sense amplifier with 18ps Setup+Hold time," in *Proc. IEEE Int. Solid-State Circuits Conf., Dig. Tech. Papers*, Feb. 2007, pp. 314–315.

- [10] J. Kim, B. S. Leibowits, J. Ren, and C. J. Madden, "Simulation and analysis of random decision errors in clocked comparators," *IEEE Trans. Circuits Syst. I, Reg. Papers*, vol. 56, no. 8, pp. 1844–1857, Aug. 2009.

- [11] T. Kobayashi, K. Nogami, T. Shiroto, and Y. Fujimoto, "A current controlled latch sense amplifier and a static power-saving input buffer for low-power architecture," *IEEE J. Solid-State Circuits*, vol. 28, no. 4, pp. 523–527, Apr. 1993.

- [12] B. J. Blalock, "Body-driving as a Low-Voltage Analog Design Technique for CMOS technology," in *Proc. IEEE Southwest Symp. Mixed-Signal Design*, Feb. 2000, pp. 113–118.