# Monograph On Field Effect Transistors

Christo Ananth,

Assistant Professor, Department of ECE, Francis Xavier Engineering College, Tirunelveli, India

JFETs- Drain and Transfer Characteristics - Current Equations - Pinch off Voltage and its significance - MOSFET - Characteristics - Threshold Voltage - Channel length modulation, D-MOSFET - E - MOSFET - Current Equation - Equivalent circuit model and its parameters, FINFET, DUAL GATE MOSFET.

### FIELD EFFECT TRANSISTOR (FET)

- \* 3 terminal semiconductor device

- \* Voltage controlled device

### **BASIC DIFFERENCE BETWEEN BJT AND FET:**

- \* BJT $\rightarrow$  bipolar device; FET  $\rightarrow$  unipolar device

- \* Current through FET is controlled by voltage whereas current through BJT is controlled by current.

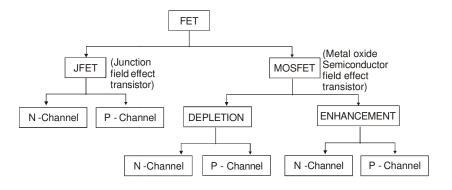

### **CLASSIFICATION OF FET:**

#### **FEATURESOFFET:**

- \* Operation of FET depends upon flow of majority carriers only.

- \* High input impedance

- \* Less noisy than BJT

- \* Simple to fabricate

- \* Occupies less space in IC's

#### **3.1.4 JUNCTION FIELD EFFECT TRANSISTOR (JFET):**

(May /June 2011 - 16 Marks, Nov/ Dec - 2010 - 16 Marks, May /June 2012 - 16 Marks)

Х

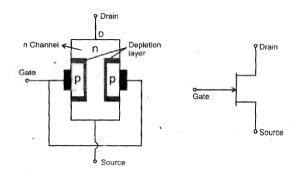

Fig 3.1 (a) n Channel JFET (b) Symbol

All Rights Reserved © 2015 IJARBEST

49

(b) Symbol

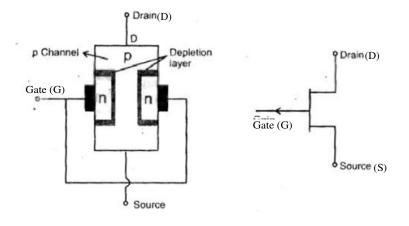

#### Fig 3.2 (a) p Channel JFET

- \* n Channel JFET consists of n type silicon bar called as "CHANNEL"

- \* 2 pieces of p-type material are attached to its sides forming *pn* junctions.

- \* Channel ends are SOURCE (S) and DRAIN (D)

SOURCE  $\rightarrow$  terminal through which majority carriers enters the bar.

$DRAIN \rightarrow$  terminal through which majority carriers leave the bar.

\* 2 p-regions are formed **by alloying** or **by diffusion** and connected together. Terminal is called **GATE**. Christo Ananth et al.[1] discussed about principles of Semiconductors which forms the basis of Electronic Devices and Components. Christo Ananth et al. [2] discussed about Improved Particle Swarm Optimization. The fuzzy filter based on particle swarm optimization is used to remove the high density image impulse noise, which occur during the transmission, data acquisition and processing. The proposed system has a fuzzy filter which has the parallel fuzzy inference mechanism, fuzzy mean process, and a fuzzy composition process. Christo Ananth et al.[3] presented a brief outline on Electronic Devices and Circuits which forms the basis of the Clampers and Diodes.

**OPERATION OF n - CHANNEL JFET :** (Nov /Dec 2012 - 8 Marks)

Fig 3.3 (a)

Fig 3.3 (b)

All Rights Reserved © 2015 IJARBEST

51

- 1) When  $V_{DS}$  fixed positive value and reverse bias on  $V_{GS}$  is increasing:

- \* Let Gate  $\rightarrow$  **not biased** and fixed positive voltage is applied between drain and source terminals.

- \* So Electrons will move through n- type channel from source to drain.

- \* When Gate  $\rightarrow$  negative biased, *pn* junctions are reverse biased and depletion regions are formed.

- \* Channel is **lightly doped**  $\Rightarrow$  Depletion region penetrates deeply into channel

- $\Rightarrow$  Effective channel width is reduced

- $\Rightarrow$  Increase in channel resistance and reduction in drain current  $I_{p}$ .

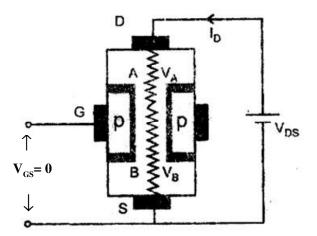

- 2.  $V_{GS} = 0$ ;  $V_{DS}$  is varied:

- \* Let  $V_{GS} = 0$ , When  $V_{DS} = 0$ , Current flowing through FET is 0 ((i.e.,  $I_D = 0$ )

- \* Channel between drain and source acts as resistance.

Fig 3.4 (a) n -CHANNEL JFET: CHANNEL REHAVING AS RESISTOR

All Rights Reserved © 2015 IJARBEST

52

Fig 3.4 (a), (b) n - Channel JFET: Channel behaving as Resistor

Fig 3.5  $V_{GS}$ =0 and  $V_{DS}$  is varied

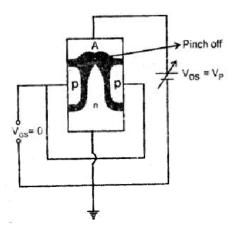

- \* Drain current I<sub>D</sub> flowing through channel causes voltage drop between drain and source.

- \* Voltage at point A > Voltage at point B

- \* Upper region of p-type material is more reverse biased than lower region.

- \* Width of depletion region near top of p-material > Width of depletion region near bottom of p-material.

- \* As  $V_{DS}$  is increased  $\Rightarrow$  Increase in reverse bias  $\Rightarrow$  Increase in width of depletion region.

- \* When channel is pinched off, conduction is blocked.

- \* Drain to source voltage at which  $I_D$  reaches  $I_{DSS}$  (Drain source saturation current) is called "**PINCH OFF VOLTAGE** ( $V_p$ )"

- \* If  $V_{DS}$  is increased beyond  $V_{p}$ ,  $I_{D}$  remains same and JFET acts as current source.

- \* If  $V_{DS}$  is further increased, a stage is reached at which gate channel junction breaks down due to avalanche effect. At this point, drain current increases rapidly and device may be destroyed.

#### CHARACTERISTICS OF JFET: (May /June - 2014 - 8 Marks)

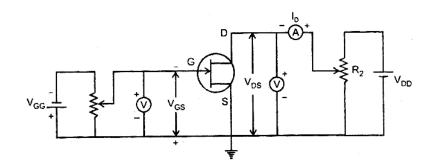

1. DRAIN Characteristics (Relation between  $I_D$  and  $V_{DS}$  for different values of  $V_{GS}$ )

2. TRANSFER Characteristics (Relation between  $I_D$  and  $V_{GS}$  for constant  $V_{DS}$ )

Х

#### FIELD EFFECT TRANSISTORS

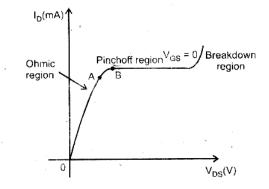

# **3.2 JFET DRAIN CHARACTERISTICS:**

UNIT - III

#### Fig 3.7 DRAIN CURRENT Vs DRAIN - SOURCE VOLTAGE ( $V_{GS}$ =0)

- \* Gate to source Voltage  $(V_{GS})$  is kept at 0 and  $V_{DS}$  is varied from 0.

- \* When  $V_{DS} = 0$ , drain current  $I_D$  is also zero.

- \* When V<sub>DS</sub> is increased, drain current starts flowing through channel and FET behaves like resistor till point A.

- \* Portion of characteristics where FET behaves like resistor is called "OHMIC REGION". FET can be used as "VOLTAGE VARIABLE RESISTOR" in ohmic region. (May /June - 2014 - 2 Marks)

- \* If V<sub>DS</sub> is increased, a stage is reached at which pinch off occurs and drain current reaches saturation level.

- \* Drain to source voltage  $(V_{DS})$  at which pinch off occurs  $\rightarrow$  **PINCH OFF VOLTAGE**  $(V_p)$  and corresponding  $I_D$  is known as  $I_{DSS}$

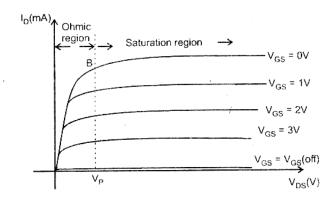

#### Fig 3.8 Drain current Vs Drain - source voltage (For different values of $V_{GS}$ )

- \* Even if  $V_{DS}$  is increased above  $V_p$ , drain current does not increase.

- Region where drain current is constant inspite of variation in V<sub>DS</sub> is called "PINCH OFF REGION"

X

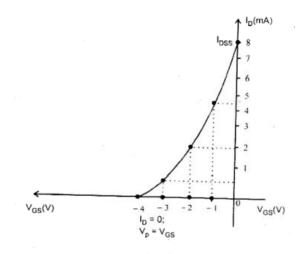

# **3.3 TRANSFER CHARACTERISTICS**

- \* Plot of drain current  $I_D$  Vs  $V_{GS}$  for constant values of  $V_{DS}$ .

- \* When  $V_{GS} = 0$ , current flowing through FET =  $I_{DSS}$

- \* When  $V_{GS} = V_{GS}(OFF)$ , drain current =0

- \* The relation between V<sub>GS</sub> (Gate to source voltage) and I<sub>D</sub> (Drain current) is given by "SHOCKLEY'S EQUATION"

$$I_D = I_{DSS} \left[ 1 - \frac{V_{GS}}{V_{GS} (OFF)} \right]^2$$

\* When  $V_{GS}$  increases, Channel Width is reduced.

When

$$V_{GS}$$

(OFF) =  $V_p$ ,

$$I_D = I_{DSS} \begin{bmatrix} V \\ 1 - V_p \end{bmatrix}^2$$

## **3.4 PARAMETERS OF JFET** (Nov /Dec 2012 -4 Marks)

Х

- 1. ac drain resistance

- 2. Transconductance

- 3. Current Amplification factor

- 4. Drain Conductance

Г

#### 1. ac DRAIN RESISTANCE $(r_d)$

\* Ratio of change in drain source voltage to change in drain current at constant gate to source voltage.

ac DRAIN RESISTANCE

$$r_{d} = \frac{\Delta V_{DS}}{\Delta I_{D}} \Big|_{V_{GS}} = \text{constant}$$

#### 2. TRANSCONDUCTANCE (g<sub>m</sub>)

\*

\*

Ratio of change in drain current to change in gate - source voltage at constant drain - source voltage.

| $\mathbf{g}_{\mathrm{m}} = -\Delta \mathbf{I}_{\mathrm{D}}$ |                           | mA/volts or micromho |

|-------------------------------------------------------------|---------------------------|----------------------|

| $\Delta V_{GS}$                                             | V <sub>DS</sub> =constant |                      |

#### 3. CURRENT AMPLIFICATION FACTOR $(\mu)$

Ratio of change in drain source voltage  $\Delta V_{GS}$  to change in gate source voltage at constant drain current.

.

Amplification Factor,

$$\mu = \frac{\Delta V_{DS}}{\Delta V_{GS}} \bigg|_{I_D} = \text{constant}$$

$$= \frac{\Delta V_{DS}}{\Delta V_{GS}}$$

$$= \frac{\Delta V_{DS}}{\Delta I_D} \frac{\Delta I_D}{\Delta V_{GS}}$$

$$= r_d g_m$$

$$\boxed{= r_d g_m}$$

Amplification Factor = ac Drain Resistance × Transconductance

4. DRAIN CONDUCTANCE (g<sub>d</sub>)

\* Reciprocal of drain resistance  $(r_d)$  is **DRAIN CONDUCTANCE**  $(g_d)$

$$g_{d} = \frac{\Delta I_{D}}{\Delta V_{DS}}$$

#### 3.5 Comparison Between FET and BJT (Nov /Dec -2012-2 Marks) (Nov /Dec 2009 -2marks)(May/June-2014 -2Marks)

| FET                                                                                                    | BJT                                                                                                                            |  |  |

|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|

| * Only 1 kind of charge carriers are responsible for conduction. It depends only on majority carriers. | * Both holes and electrons are responsible for<br>conduction of current. It depends on both<br>majority and minority carriers. |  |  |

| * FET has 2 junctions⇒less noisy.                                                                      | * BJT is noisy because of single junction.                                                                                     |  |  |

| * FET $\rightarrow$ Voltage controlled device.                                                         | * BJT $\rightarrow$ current controlled device.                                                                                 |  |  |

| * Negative temperature coefficient.                                                                    | * Positive temperature coefficient                                                                                             |  |  |

| * No thermal breakdown                                                                                 | * Has thermal breakdown                                                                                                        |  |  |

| * Easy to fabricate                                                                                    | * Fabrication is difficult                                                                                                     |  |  |

| * Higher voltage gain                                                                                  | *Low voltage gain                                                                                                              |  |  |

# \_\_\_\_\_\_\_x 3.6 EXPRESSION FOR DRAIN CURRENT (CURRENT EQUATIONS)

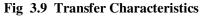

#### Fig. 3.10 TRANSFER CHARACTERISTICS OF JFET

\* Drain source Voltage  $(V_{DS})$  is kept constant and gate source voltage  $(V_{GS})$  is varied.

\* For different values of  $V_{GS}$ , drain current is plotted.  $V_{GS}$  is decreased from zero till  $I_D$  is reduced to 0.

From Shockley's equation,

$$I_D = I_{DSS} \left( 1 - \frac{V_{GS}}{V_P} \right)^2 \rightarrow \mathbb{O}$$

where  $I_D = drain current$

$$I_{DSS} = Value \text{ of } I_D \text{ when } V_{GS} = 0$$

$V_{p}$  = Pinch off voltage

$$\frac{\partial I_D}{\partial V_{GS}} = I_{DSS} \left[ 2 \left( 1 - \frac{V_{GS}}{V_P} \right) \left( \frac{-1}{V_P} \right) \right]$$

$$= \frac{-2I}{\frac{DSS}{V_P}} \left( 1 - \frac{GS}{V_P} \right)$$

We know that

$$g_{m} = \frac{\partial I_{D}}{\partial V_{GS}} \bigg|_{V_{DS} = \text{constant}}$$

$$g_{m} = \frac{-2I_{DSS}}{V_{P}} \bigg( \frac{V}{1 - \frac{GS}{V_{P}}} \bigg) \longrightarrow \textcircled{2}$$

From<sup>①</sup>,

$$1 - \frac{V_{GS}}{V_P} = \sqrt{\left(\begin{array}{c}I\\I_{DSS}\end{array}\right)}$$

$$\therefore g_m = \frac{-2I_{DSS}}{V_P}\sqrt{\frac{I_D}{I_{DSS}}}$$

$$g_m = \frac{-2\sqrt{I_{DSS}} I_D}{V_P}$$

When  $V_{GS} = 0$ ,  $g_m = g_{m0}$

$$\textcircled{2} \Rightarrow \therefore g_{m 0} = \frac{-2 I_{DSS}}{V_P}$$

$$\boxed{g_m = g_{m 0} \begin{pmatrix} V \\ 1 - \frac{GS}{V_P} \end{pmatrix}}$$

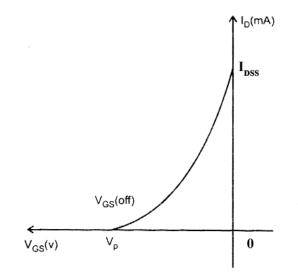

SLOPE OF TRANSFER CHARACTERISTICS AT  $\mathbf{I}_{\text{DSS}}$ :

#### Fig.3.11 SLOPE OF TRANSFER CHARACTERISTICS

\* To find slope of transfer characteristics at  $I_{DSS}$ , draw tangent line to characteristics at  $I_{DSS}$

\* Slope can be obtained by differentiating Shockley equation and then substitute

$$I_D = I_{DSS}$$

$$Slope = \frac{y_2 - y_1}{x_2 - x_1}$$

$$= \frac{I_{DSS} - 0}{0 - (-V_{GS})}$$

$$Slope = \frac{I_{DSS}}{V_{GS}}$$

Shockley's equation is

$$I_{D} = I_{DSS} \left( 1 - \frac{V_{GS}}{V_{P}} \right)^{2}$$

$$\frac{\partial_{I_{D}}}{\partial V_{GS}} = \frac{-2 I_{DSS}}{V_{P}} \left( 1 - \frac{V_{GS}}{V_{P}} \right)$$

$$= \frac{-2 I_{DSS}}{V_{P}} \sqrt{\frac{I_{D}}{I_{DSS}}}$$

Substitute  $I_D = I_{DSS}$

$$\frac{\partial I_D}{\partial V_{GS}} = \frac{-2I_{DSS}}{V_P} = \frac{I_{DSS}}{(-V_P/2)}$$

\* To find the value of pinch - off voltage, tangent is drawn to current at  $I_D = I_{DSS}$  and its intercept is found for 2 times on  $V_{GS}$  axis which is equal to  $V_P$ .

#### APPLICATIONS OF JFET (May / June 2014-6Marks)

- $\rightarrow$  FET  $\rightarrow$ high input impedence which is used as input circuit for instrument and audio applications.

- → Voltage Variable Resistor in amplifiers

$\rightarrow Level shifter between 2 operational amplifiers operating at different supply voltages.$  $<math display="block"> \rightarrow nixie tube drivers$  **x**

#### 3.7 MOSFET (METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR

$\rightarrow$  3 terminal device (source, gate, drain)

- → Gate of MOSFET is insulated from channel. So MOSFET is also known as "IGFET"(Insulated gate FET)

- $\rightarrow$  no pn structure; Gate of MOSFET is insulated from channel by SiO<sub>2</sub> layer.

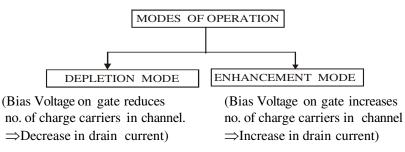

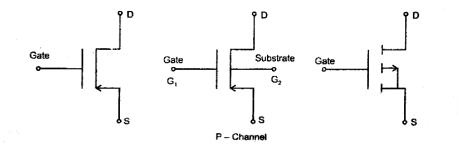

#### DEPLETION MOSFET (D- MOSFET) (Nov / Dec -2010 - 8 Marks) (May/ June -2012 - 2 Marks) (Nov/Dec -2009 - 8 Marks) (May / June - 2010-8 Marks)

\* Operate in both depletion and enhancement modes.

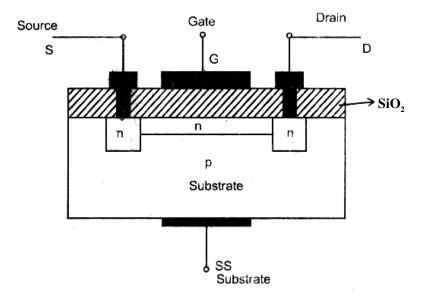

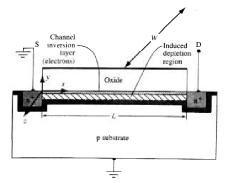

#### Fig 3.12 n -CHANNEL DEPLETION MOSFET

- \* It consists of lightly doped p- type substrate in which two highly doped n- regions are diffused. Two heavily doped n-regions act as Source and Drain.

- \* Lightly doped n-type channel is introduced between 2 heavily doped source and drain.

- \* Thin layer (of 1 m thickness) if  $SiO_2$  is coated on the surface.

- \* Holes are cut in oxide layer to make contact with 'n' regions.

- \* Due to  $SiO_2$ , gate is completely insulated from channel.

- \* In some MOSFET's, p type substrate is internally connected to source, whereas in many discrete devices, additional terminal is provided for substrate labeled SS.

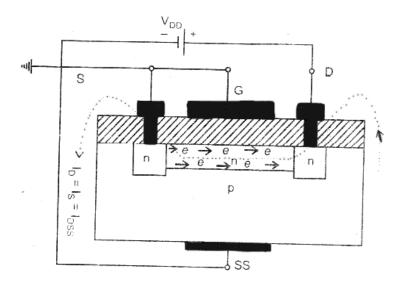

#### A) BASIC OPERATION OF D-MOSFET

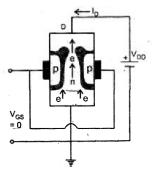

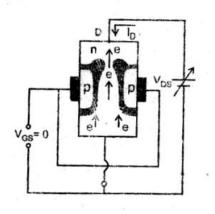

# Fig . 3.13 n - CHANNEL DEPLETION MOSFET with $V_{\rm GS}$ = 0 AND APPLIED VOLTAGE $V_{\rm DD}$

- \* Voltage  $V_{DS}$  is applied between drain and source terminal and  $V_{GS} = 0$

- \* Therefore, current is established from drain to source similar to JFET. Saturated drain current I<sub>DSS</sub> flows during pinchoff.

- \* If negative voltage is applied to gate w.r.t source, holes are introduced in channel.

- \* Holes recombine with electrons and reduce no. of free electrons in n- channel available for conduction.

- \* Negative bias ⇒less no. of free electrons in channel

- \* Negative voltage on gate deplete the channel, so the device is called "DEPLETION MOSFET"

- \* When sufficient negative voltage is applied to gate, channel may be completely cutoff and corresponding  $V_{GS}$  is called " $V_{GS}$  (OFF)"

- \* If positive voltage is applied to gate w.r.t. source, electrons are induced in channel. Induced electrons constitute additional current from source to drain.

- \* If V<sub>GS</sub> is increased more in positive direction, more no.of electrons are induced⇒ Increase in drain current.

- \* Mode in which MOSFET operates for positive values of gate to source voltage → "ENHANCEMENT MODE"

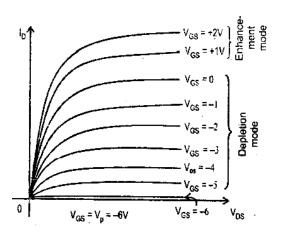

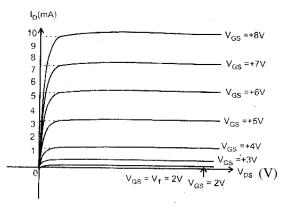

#### **B)** CHARACTERISTICS OF DEPLETION MOSFET

#### (1) DRAIN CHARACTERISTICS:

→ Plot of drain current Vs Drain - source Voltage for various values of Gate- Source Voltage.

Fig 3.14 I<sub>D</sub> Vs V<sub>DS</sub>

- $\rightarrow$  For negative value of V<sub>GS</sub>, characteristics of depletion MOSFET is similar to N- Channel JFET.

- → If Gate is made positive, additional carriers are introduced in channel and CHANNEL CONDUCTIVITY increases.

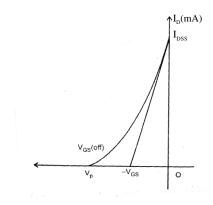

#### **C) TRANSFER CHARACTERISTICS:**

Fig 3.15  $I_D Vs V_{GS}$

\* Depletion MOSFET can be operated with  $V_{GS} > 0$

Fig 3.16 CIRCUIT SYMBOLS FOR n -CHANNEL MOSFET

ENHANCEMENT MOSFET (May/June - 2011 - 8 Marks) (May/June - 2010 - 8 Marks)(Nov / Dec -2010 - 8 Marks) (Nov/Dec -2009 - 8 Marks) (May /June - 2012 - 2 Marks)

\* It consists of p-type substrate and 2 heavily doped n-regions that act as source and drain (similar to **DEPLETION MOSFET**)

- \* SiO<sub>2</sub> layer isolates gate from region between drain and source.

- \* Source and drain terminals are connected through metallic contacts to n-doped regions.

- \* Enhancement MOSFET does not contain diffused channel between source and drain.

#### WORKING:

- \* When drain is made positive w.r.t source and no potential is applied to gate, a small drain current ((i.e) a reverse leakage current) flows.

- \* If positive voltage is applied to gate w.r.t source and substate, negative charge carriers are induced in substrate.

- \* Negative charge carriers (MINORITY CARRIERS) in p substrate form "INVERSION LAYER"

- \* As gate potential is increased, more and more negative charge carriers are induced.

- \* Negative carriers that are accumulated between source and drain constitute n-type channel.

- \* Drain current flows from source to drain through induced channel.

- \* Magnitude of drain current depends on Gate potential.

- \* Conduction of channel is enhanced by positive bias voltage on gate, so the device is known as **"ENHANCEMENT MOSFET"**

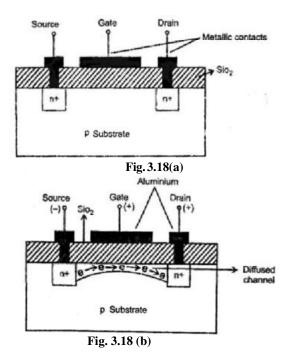

#### **A) DRAIN CHARACTERISTICS**

#### Fig 3.19 DRAIN CHARACTERISTICS

- \*  $I_{DSS}$  for  $V_{GS} = 0$  is very small (nA)

- \* Drain current increases with positive increase in gate source bias voltage. All Rights Reserved © 2015 IJARBEST

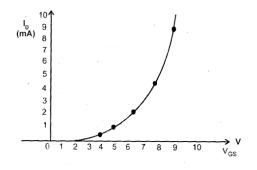

#### **B) TRANSFER CHARACTERISTICS:**

#### Fig 3.20 TRANSFER CHARACTERISTICS

- \* As V<sub>GS</sub> is made positive, current I<sub>D</sub> increases slowly and then more rapidly with increase in V<sub>GS</sub>.

\* Gate source Voltage at which there is significant increase in drain current is called

- THRESHOLD VOLTAGE  $(V_T \text{ or } V_{GS(th)})$

#### C) EQUATION FOR TRANSFER CHARACTERISTICS:

| $I_{\rm D} = k(V_{\rm GS} - V_{\rm GS})$ | (th))2 |

|------------------------------------------|--------|

|------------------------------------------|--------|

#### COMPARISON BETWEEN JFET AND MOSFET (Nov /Dec -2010 - 2Marks)

| JFET                                                                                                                                  | MOSFET                                                                                                                                                    |  |

|---------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| → Input resistance is of the order of $10^9 \Omega$<br>because no insulating layer is present<br>between gate and conducting channel. | $\rightarrow$ Input resistance is very high in order of 10 <sup>13</sup> Ω<br>because insulation layer is present between<br>gate and conducting channel. |  |

| →Gate leakage current is of order of 0.1 to 10mA                                                                                      | $\rightarrow$ Gate leakage current is of order of 0.1 to 10pA                                                                                             |  |

| $\rightarrow$ Drain resistance is of order of 0.1 to<br>1M Ω .                                                                        | $\rightarrow$ Drain resistance is of order of 1 to 50 K $\Omega$                                                                                          |  |

| $\rightarrow$ Operates only in depletion mode.                                                                                        | → Operates both in enhancement and depletion modes                                                                                                        |  |

| $\rightarrow$ Electric field across reverse biased pn                                                                                 | $\rightarrow$ Electric field across insulating layer controls                                                                                             |  |

| junction controls Conductivity of channel                                                                                             | Conductivity of channel.                                                                                                                                  |  |

#### 3.9. COMPARISON BETWEEN N- CHANNEL AND P-CHANNEL MOSFETs

|                                                                           | P-CHANNEL MOSFET                                                          |   | N- CHANNEL MOSFET                                                      |

|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---|------------------------------------------------------------------------|

| <ul> <li>Occupies 2 times more area than<br/>n- channel MOSFET</li> </ul> |                                                                           | * | Occupies 2 times less area than p-channel MOSFET                       |

| *                                                                         | Packing density of p-channel<br>MOSFET is less than n- channel<br>MOSFET. | * | Packing density of n- channel MOSFET is<br>more than p- channel MOSFET |

| *                                                                         | Slower than n- channel MOSFET                                             | * | Faster than p-channel MOSFET.                                          |

| *                                                                         | p-MOS devices are bigger than<br>n- MOS devices.                          | * | n- MOS devices are smaller than p-MOS devices                          |

#### 3.10 COMPARISON BETWEEN p-CHANNEL JFET AND n-CHANNEL JFET (May /June 2010 - 2Marks)

|                                                                                         | p - Channel JFET                                            |   | n - channel JFET                                                 |  |

|-----------------------------------------------------------------------------------------|-------------------------------------------------------------|---|------------------------------------------------------------------|--|

| *                                                                                       | Current carriers $\rightarrow$ holes                        | * | Current carriers $\rightarrow$ electrons                         |  |

| <ul> <li>Channel is made of p-type material<br/>and gate of n-type material.</li> </ul> |                                                             | * | Channel is made of n-type material and gate of p- type material. |  |

| *                                                                                       | Symbol has arrow pointing away from drain / source channel. | * | Symbol has arrow pointing towards drain / source channel.        |  |

| *                                                                                       | More noise produced                                         | * | Less noise produced                                              |  |

| *                                                                                       | Less Transconductance                                       | * | Large transconductance                                           |  |

| _                                                                                       | x                                                           |   |                                                                  |  |

#### **3.11 THRESHOLD VOLTAGE OF MOSFET:**

- \* DEFINITION : Threshold Voltage is defined as the applied gate Voltage required to achieve threshold inversion point. Christo Ananth et al. [4] discussed about PN junction diode, Current equations, Diffusion and drift current densities, forward and reverse bias characteristics and Switching Characteristics of Semiconductor Diodes. Christo Ananth et al.[5] analyzed NPN, PNP Junctions, Early effect, Current equations, Input and Output characteristics of CE, CB CC, Hybrid -π model, h-parameter model, Ebers Moll Model, Gummel Poon-model and Multi Emitter Transistor in Bipolar Junctions.

- \* Threshold inversion point is defined as the condition when surface potential is

$_{s} = 2$   $_{fp}$  for p- type semiconductor &  $_{s} = 2$   $_{fn}$  for n - type semiconductor.

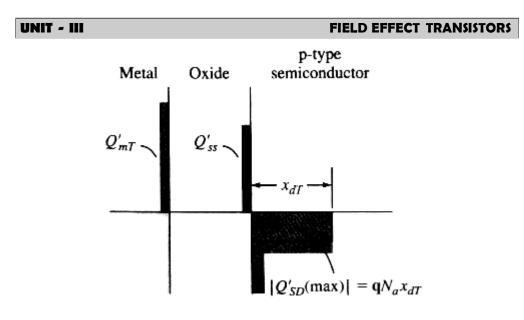

#### Fig 3.21 CHARGE DISTRIBUTION THROUGH MOS DEVICE AT THRESHOLD INVERSION POINT FOR p- TYPE SEMICONDUCTOR SUBSTRATE

\* Equivalent oxide charge  $\rightarrow Q'_{ss}$

\* Positive charge on metal plate at threshold  $\rightarrow Q'_{\rm mT}$

$$Q'_{mT} + Q'_{SS} = |Q'_{SD} (max)|$$

where  $|Q'_{SD}(max)| = qN_a x_{dT}$

$|Q'_{SD}(max)| \rightarrow$  magnitude of maximum space charge density per unit area of depletion region.

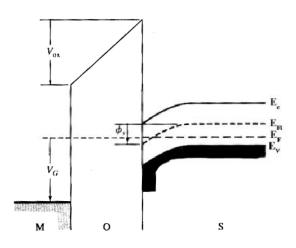

#### Fig 3.22 ENERGY BAND DIAGRAM THROUGH MOS STRUCTURE WITH POSITIVE APPLIED GATE BIAS

\* Applied gate Voltage will change voltage across oxide and will change surface potential.

Gate Voltage  $V_G = \Delta V_{OX} + \Delta$  s

$$= V_{OX} + s + ms$$

At threshold,  $V_G = V_{TN} (V_{TN} \rightarrow \text{threshold voltage which creates electron inversion layer charge.})$

Surface potential  $_{s} = 2$   $_{fp}$  at threshold

$$\therefore V_{TN} = V_{OXT} + 2_{fp} + _{ms}$$

where  $V_{\text{OXT}}$  is Voltage across oxide at threshold inversion point.

\*  $V_{\text{OXT}}$  is related to charge on metal (  $Q'_{\text{mT}}$ )and oxide capacitance ( $C_{\text{OX}}$ )

$$V_{OXT} = \frac{Q'}{C_{mT}}$$

ox

$$V_{OXT} = \frac{Q'_{mT}}{C_{OX}} = \frac{1}{C_{OX}} (|Q'_{SD} (\max)| - Q'_{SS})$$

Threshold Voltage

$$V_{TN} = \frac{\downarrow Q'_{SD} (\max) \downarrow}{C_{OX}} = \frac{Q'_{SS}}{C_{OX}} + \frac{\downarrow}{ms} + 2 \qquad fp$$

All Rights Reserved © 2015 IJARBEST

(or)

$$V_{\rm TN} = (|Q'_{\rm SD} (\rm max)| - Q'_{\rm SS}) \frac{t_{OX}}{C_{OX}} + \frac{1}{ms} + 2 f_{\rm p}$$

. .

\* **Flat Band Voltage** is defined as applied gate Voltage such that there is no band bending in semiconductor. So there is zero net space charge in the region.

$$V_{FB} = \underset{C}{M} \Box \frac{Q'_{SS}}{C_{OX}}$$

$$\therefore V_{TN} = \frac{Q'_{SD}(\max)}{C_{OX}} + V_{FB} + 2_{fp}$$

- \* Negative Voltage must be applied to gate to make inversion layer charge equal to zero; Positive gate Voltage will induce larger inversion layer charge.

- \* For p-side,

$$V_{TP} = \left( \frac{1}{2} Q_{SD}^{\prime} (max) - Q^{\prime} ss \right) \left( \frac{t_{ox}}{C_{ox}} \right) + \phi_{ms} - 2\phi_{fn}$$

where  $m_{m} = - + \frac{E^{g}}{2q} - \frac{1}{2q} + \frac{E^{g}}{2q} + \frac{1}{2q} + \frac{1}{$

$$|\mathbf{Q}'_{\mathrm{SD}}(\mathrm{max})| = q \mathbf{N}_{\mathrm{d}} x_{\mathrm{dT}}$$

where

$$x_{dT} = \left[\frac{4}{qN_d}\right]^{1/2}$$

$$m_{fn} = V_t \ln\left(\left|\frac{N_d}{n_i}\right|\right)$$

$V_{TP} \rightarrow$  threshold voltage which induces inversion layer of holes.

\_\_\_\_\_ x -

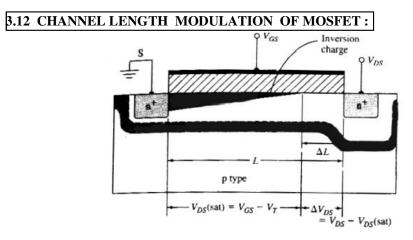

Depletion Width extending into p-region of pn junction (under zero bias)

$$x_p = \frac{2 s_{fp}}{qN_a}$$

Space charge width of Drain - substrate junction  $x_p = \frac{2}{qN_a} (r_{fp} + V_{DS})$

\* Space charge region defined by  $\Delta L$  does not form until  $V_{DS} > V_{DS}$  (sat)  $\Delta L$  = Total space charge width - Space charge width when  $V_{DS} = V_{DS}$  (sat)

$$\Delta L = \sqrt{\frac{2}{qN_a}} \left( \sqrt{\frac{1}{p} + V_{DS}(sat) + \Delta V_{DS}} - \sqrt{\frac{1}{p} + V_{DS}(sat)} \right)$$

where  $\Delta V_{DS} = V_{DS} - V_{DS}$  (sat)

Electric field E  $_{sat}$   $\rightarrow$  electric field at the point where inversion layer charge is pinched off.

$$\frac{dE}{dx} = \frac{(x)}{s}$$

where  $\rho(x) = -qN_a$ Integrating this equation,

$$E = \frac{-qN_a x}{s} = -E_{sat}$$

Potential  $(x) = -\int E dx$

$$=\frac{qN_ax^2}{2_s}+E_{sat}x+C$$

where C → integration constant \* **BOUNDARY CONDITIONS :**

$$(x = 0) = V_{DS}(sat)$$

$(x = \Delta L) = V_{DS}$

Substituting the boundary conditions,

$$V_{DS} = \frac{qN_{a}(\Delta L)^{2}}{2} + E_{sat}(\Delta L) + V_{DS}(sat)$$

$$V_{DS} = (\Delta L)^{2} \begin{bmatrix} qN_{a} \\ 2 \end{bmatrix} + V \quad (sat)(\because Neglecting E_{sat})$$

$$(\Delta L)^{2} \left(\frac{qN_{A}}{2s}\right) = V - V \quad (sat)$$

$$(\Delta L) = \sqrt{\frac{2\xi_{S}}{qN_{a}}} \left(\sqrt{\varphi_{sat}} + (V_{DS} \Box_{DS} \quad (sMt) - \sqrt{\varphi_{sat}}\right)$$

where

$$= \frac{2}{sat} \left(\frac{E^{2}_{sat}}{qN_{a}}\right) = V - V \quad (sat)$$

\* Drain current is inversely proportional to channel length

$$\mathbf{I}_{\mathrm{D}}^{'} = \left(\frac{L}{L - \Delta L}\right) \mathbf{I}_{\mathrm{D}}$$

$I_{D}$   $\rightarrow$  actual drain current

$I_{D} \rightarrow ideal drain current$

- \*  $I_{_{D}}$  is a function of  $V_{_{DS}}$  even though the transistor is biased in saturation region.

- \* When MOSFET dimensions becomes small,  $\Delta L$  becomes large and Channel length modulation becomes very severe.

\_\_\_\_\_ x \_\_\_\_\_

#### UNIT - III

#### FIELD EFFECT TRANSISTORS

#### 3.13 CURRENT EQUATIONS OF MOSFET

#### **ASSUMPTION :**

$\rightarrow$  Current in channel is due to drift rather than diffusion.

$\rightarrow$  There is no current through gate oxide

$\rightarrow$ Any fixed oxide charge is an equivalent charge density at oxide - semiconductor interface.

$\rightarrow$ Carrier mobility in channel is constant.

#### Fig 3.24 MOSFET STRUCTURE

By Ohm's law,

$\begin{bmatrix} J_x = & E_x \\ where & \longrightarrow \end{bmatrix}$  Channel Conductivity  $E_x \rightarrow \text{Electric field along channel}$

$$= q_{n} n(y)$$

where  $_{n} \rightarrow$  electron mobility

$n(y) \rightarrow$  electron concentration in inversion layer.

Total channel current

$$I_x = \int_y \int_z J_x dy dz$$

Inversion layer charge per unit area =  $Q'_n = -\int q n(y) dy$

$$I_x = -W \quad {}_nQ'_nE_x$$

where  $W \rightarrow Channel width$ By charge neutrality:

$$Q'_{m}+Q'_{SS}+Q'_{n}+Q'_{SD}$$

(max) = 0  $\rightarrow$  ①

where  $Q'_m \rightarrow$  Charge on metal plate

$Q'_{ss} \rightarrow$ Equivalent oxide charge

$Q'_n \rightarrow$  Inversion layer charge per unit area

$Q'_{SD(\max)} \rightarrow$ maximum space charge density per unit area By Gauss's law,

$$\oint_{S} \xi E_{n} dS = Q_{T} \longrightarrow \bigcirc$$

where  $Q_T \rightarrow total$  charge enclosed by surface 'S'.

$E_n \rightarrow$ normal component of electric field crossing surface 'S'.

$$\oint_{S} \xi E_n dS = - _{OX} E_{OX} W dx = Q_T \longrightarrow \Im$$

where  $_{OX} \rightarrow$  permittivity of oxide

Total charge enclosed  $Q_{T} = \left[Q'_{ss} + Q'_{n} + Q'_{sD(max)}\right] W dx$

$$\therefore -\xi_{OX} E_{OX} W dx = \left[ Q_{SS}' + Q'_{n} + Q'_{SD (max)} \right] W dx$$

$$- \sum_{OX} E_{OX} = Q_{SS}' + Q_{n}' + Q'_{SD (max)} \longrightarrow \textcircled{4}$$

Fermi level in p-type semiconductor $\rightarrow E_{FP}$ Fermi level in metal $\rightarrow E_{FM}$

$$E_{FP}-E_{FM} = q(V_{GS}-V_x)$$

$$(V_{GS}-V_x) = V_{OX}+2_{fp}+ m_s \rightarrow \texttt{S}$$

$\rightarrow 6$

$(V_{GS} - V_x) = V_{OX} + V_{ox}$ Electric field in oxide  $E_{OX} = \frac{V_{ox}}{t_{ox}}$

We already know

$$I_{x} = -W \underset{n}{\overset{n}{\bigcup}} Q_{n} E_{x}$$

$$I_{x} = -W \underset{n}{\bigcup} C_{ox} V/dx [(V_{GS} - V_{x}) - V_{T}] \longrightarrow \textcircled{O}$$

where  $E_x = \frac{-dV_x}{dx}$  $V_T \rightarrow$ threshold voltage

=

$$(|Q_{SD}'(max)| - Q_{SS}') \begin{pmatrix} t_{ox} \\ ox \end{pmatrix} + m_s + 2 m_s + 2 p_{fp}$$

(by threshold voltage equation)

From ⑦

Integrating ⑦,

$$\int_{0}^{L} I_{x} dx = -W \int_{0}^{R} C_{OX} \int_{V_{x(0)}}^{V_{x(L)}} (V_{GS} - V_{T}) - V_{x} dV_{x} \longrightarrow$$

The expression for drain current is

$$I_{D} = \frac{W_{-n}C_{OX}}{2L} \left[ 2(V_{GS} - V_{T})V_{DS} - V_{DS}^{2} \right] \rightarrow \mathfrak{D}$$

$$I_{D}(sat) = \frac{W_{-n}C_{OX}}{2L} \left[ 2(V_{GS} - V_{T})V_{DS}(sat) - V_{DS}^{2}(sat) \right]$$

$$V_{DS} = V_{GS} - V_{T}$$

$$\therefore I = \frac{W_{-n}C_{OX}}{C_{OX}} - V(V - V) - (V - V)^{2} \right]$$

$$\left[ 2(V_{-1})^{-1} - \frac{GS}{2L} \left[ 2(V_{-N})^{2} - (V_{-N})^{2} - (V_{-N})^{2} \right]$$

$$= \frac{W_{-n}^{2}C_{OX}}{2L} \left[ 2(V_{-N})^{2} - (V_{-N})^{2} \right]$$

$$This is the ideal current equation in saturated region$$

This is the ideal current equation in saturated region. Х

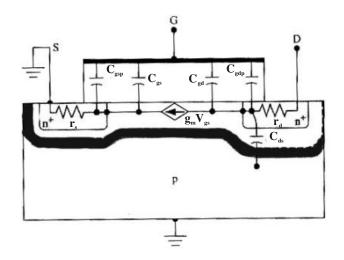

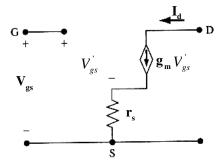

#### 3.14 EQUIVALENT CIRCUIT MODEL AND ITS PARAMETERS:

- \* Source and substrate are both connected to ground potential.

- \*  $C_{gs} \rightarrow gate to substrate pn junction capacitance.$

- \*  $C_{gd}^{gs} \rightarrow$  gate to drain pn junction capacitance \*  $C_{gsp} \rightarrow$  gate to substrate parasitic or overlap capacitance \*  $C_{gdp} \rightarrow$  gate to drain parasitic or overlap capacitance  $\rightarrow$  lowers frequency response of device.

Fig 3.25 RESISTANCES AND CAPACITANCES IN n- CHANNEL MOSFET STRUCTURE

$C_{ds} \rightarrow drain$  - to - substrate pn junction capacitance  $r_{s}, r_{d} \rightarrow$  series resistances associated with source and drain terminals.

Fig 3.26 SMALL SIGNAL EQUIVALENT CIRCUIT

$V_{gs} \rightarrow$  Internal gate to source voltage which controls channel current  $C_{gsT} \rightarrow$ Gate to - source total capacitance

$C_{gdT} \rightarrow Gate - to - drain total capacitance$

$r_{_{ds}} ~ \rightarrow drain$  - to source resistance which is associated with slope  $I_{_D} Vs \; V_{_{DS}} ~$  .

\*  $r_{ds}$  is finite because of Channel length modulation.

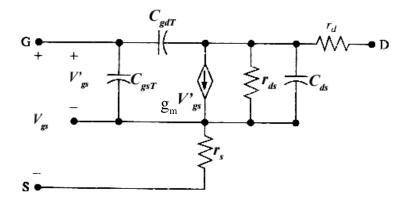

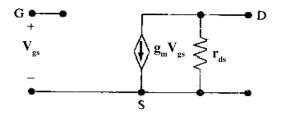

#### Fig 3.27 SIMPLIFIED SMALL - SIGNAL EQUIVALENT CIRCUIT

- \* Here r<sub>s</sub> and r<sub>d</sub> resistances are neglected, So Drain current is a function of gate to source voltage through transconductance.

- \* Input gate impedance  $\rightarrow$  infinite

Fig 3.28 SMALL SIGNAL EQUIVALENT CIRCUIT INCLUDING SOURCE RESISTANCE  $\rm r_s$

\* Here  $r_s$  is included and  $r_{ds}$  is neglected.

Drain current  $I_d = g_m V_{gs} \rightarrow \mathbb{O}$

Relation between  $V_{gs}$  and  $V_{gs}^{'}$  is

$$V_{gs} = V_{gs} + [g_m V_{gs}]r_s$$

$$V_{gs} = [1 + g_m r] V_{gs} \rightarrow 0$$

All Rights Reserved © 2015 IJARBEST

r<sub>ds</sub>

Subs 2 in 1

\* Equivalent circuit of p - channel MOSFET is just the same as n- channel MOSFET except that Voltage polarities and current directions are reversed. 3.14.1 PARAMETERS OF EQUIVALENT CIRCUIT MODEL:

#### 1. VOLTAGE GAIN (A<sub>v</sub>)

Voltage gain (A<sub>V</sub>) =  $\frac{V_0}{V_i}$

\* Ratio of output voltage to input voltage  $\rightarrow A_v$

$$V_{0} = -g_{m} V_{gs} (r_{d} \parallel R_{D})$$

$$V_{0} = -g_{m} V_{i} (r_{d} \parallel R_{D}) (\because V_{gs} = V_{i} = \text{input voltage})$$

$$\frac{V_{0}}{V_{i}} = -g_{m} (r_{d} \parallel R_{D})$$

$$A_{V} = -g_{m} (r_{d} \parallel R_{D})$$

If  $R_D > r_d$ ,

$$A_v = -g_m R_D$$

2. INPUT IMPEDANCE (Z<sub>i</sub>)

$$Z_i = r_s$$

3. OUTPUT IMPEDANCE (Z<sub>0</sub>)

$$\mathbf{Z}_0 = \mathbf{r}_{\mathrm{ds}} \parallel \mathbf{r}_{\mathrm{d}}$$

If

$$r_{ds} > r_d$$

$$Z_0 = r_{ds}$$

#### 4. INPUT CAPACITANCE (MILLER CAPACITANCE)

$C_i = C_{gs} + (1 + g_m R_d) C_{gd}$

\_\_\_\_\_ x

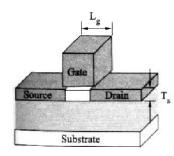

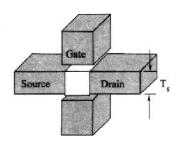

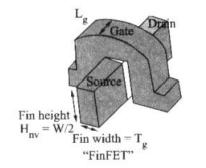

### 3.15 FINFET (May/June-2014-4Marks)

- \* **FINFET** Multiple gate field effect transistor (MUGFET) or a multiple device which incorporates more than one gate into single device.

- \* Multiple gates are controlled by single gate electrode.

- \* Multiple gate device employing independent gate electrodes = Multiple Independent Gate Field Effect Transistor (MIGFET)

- \* "Fin" narrow channel between source and drain.

- \* The thin body MOSFET structure **controls short channel Effects** and **suppresses leakage** by keeping gate capacitance in close proximity to channel.

Ultra-Thin Body (UTB)

Double-Gate (DG)

#### Fig 3.29 DOUBLE GATE FINFET DEVICE

All Rights Reserved © 2015 IJARBEST

- \* Planar Double gate MOSFET structure is rotated 90° to provide lowest gate leakage current and enables easy manufacturing using standard lithography techniques because gate electrodes are self aligned.

- \* The Gate has control over conducting channel which allows very small leakage current when device is in OFF state.

- \* This results in low threshold voltages which results in greater switching speed.

- \* FINFETs  $\rightarrow$  37% faster than planar devices.

- \* FINFETs  $\rightarrow$  balances throughput performance and power.

#### **ADVANTAGES:**

- $\rightarrow$  Improved frequency performance

- $\rightarrow$  Reduced capacitance

- $\rightarrow$  High drive current

- $\rightarrow$  Reduction in interconnect length

- $\rightarrow$  Minimizes Noise and latchup

#### DISADVANTAGES

- $\rightarrow$  Quantized widths

- $\rightarrow$  Bulk in size $\Rightarrow$  Problems of self Heating and dissipation of power.

\_\_\_\_\_ x \_\_

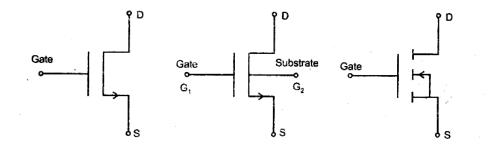

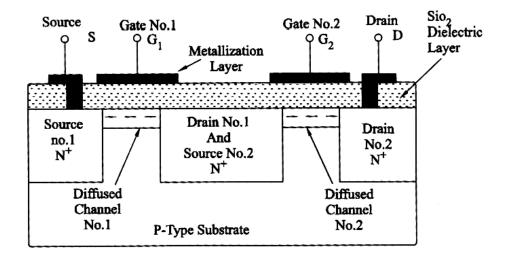

### 3.16 DUAL GATE MOSFET (May/June -2014 - 4 Marks)

- → Dual Gate MOSFET or double gate transistor is an N-Channel enhancement type, dual insulated gate FET which utilizes MOS construction.

- $\rightarrow$  Consists of 2 equal dual gate MOSFET with shared source and gate leads.

- $\rightarrow$  Source and substrate are interconnected.

- → Internal bias circuits enable DC stabilization and good cross modulation performance during automatic Gain control.

- $\rightarrow$  The transistor has micro miniature plastic package.

#### Fig 3.30 DUAL GATE N-CHANNEL DEPLETION MOSFET

- \* Dual Gate MOSFET has tetrode configuration where both gates control the current in the device.

- \* Used for small signal devices in RF applications.

- \* Biasing drain side gate at constant potential reduces gain loss caused by Miller effect.

- \* Tetrode configuration does not replicate vacuum tube tetrode.

- \* Vacuum tube tetrodes exhibit lower grid plate capacitance and high output impedance with high voltage gain than triode Vacuum tubes.

#### **3.16.1 SALIENT FEATURES**

- $\rightarrow$  2 AGC amplifiers in 1 package

- $\rightarrow$  High AGC range, high gain, low noise figure.

- $\rightarrow$  Integrated gate protection diodes.

#### **ADVANTAGES**

- \* Better control over short channel effects.

- \* Advantageous over existing fabrication processes.

- \* High current driving capability

- \* Uniformity of Silicon channel thickness

#### DISADVANTAGES

$\rightarrow$  Accessing bottom gate for device wiring is not easy.

- $\rightarrow$  Front and back gates cannot be independently biased.

- $\rightarrow$  Fabrication of back gate and gate dielectric below Silicon channel is difficult.

#### APPLICATIONS

- $\rightarrow$  2 gain controlled input stage for UHF and VHF tuners.

- $\rightarrow$  Professional communication equipment.

#### – x – References

Christo Ananth, S.Esakki Rajavel, S.Allwin Devaraj, P.Kannan. "Electronic Devices.", ACES Publishers, Tirunelveli, India, ISBN: 978-81-910-747-6-5, Volume 2, December 2014, pp:1-300.

[2] Christo Ananth, Vivek.T, Selvakumar.S., Sakthi Kannan.S., Sankara Narayanan.D, "Impulse Noise Removal using Improved Particle Swarm Optimization", International Journal of Advanced Research in Electronics and Communication Engineering (IJARECE), Volume 3, Issue 4, April 2014,pp 366-370

[3] Christo Ananth, W.Stalin Jacob, P.Jenifer Darling Rosita. "A Brief Outline On ELECTRONIC DEVICES & CIRCUITS.", ACES Publishers, Tirunelveli, India, ISBN: 978-81-910-747-7-2, Volume 3, April 2016, pp:1-300.

[4] Christo Ananth, "Monograph On Semi Conductor Diodes", International Journal of Advanced Research in Biology, Ecology, Science and Technology (IJARBEST), Volume 1, Issue 3, June 2015, pp:40-63.

[5] Christo Ananth, "Monograph On Bipolar Junctions", International Journal of Advanced Research in Biology, Ecology, Science and Technology (IJARBEST), Volume 1, Issue 4, July 2015, pp:28-93.